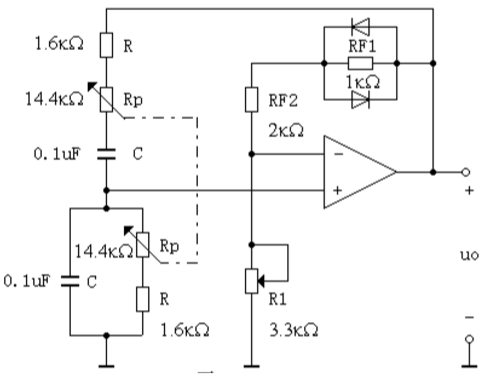

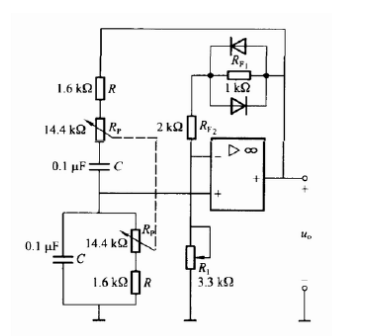

如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R=1.6kΩ,C=0.1μF,R3=3.3kΩ,Rf1=1kΩ,Rf2=2kΩ。

如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R=1.6kΩ,C=0.1μF,R3=3.3kΩ,Rf1=1kΩ,Rf2=2kΩ。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R=1.6kΩ,C=0.1μF,R3=3.3kΩ,Rf1=1kΩ,Rf2=2kΩ。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R…”相关的问题

更多“如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R…”相关的问题

第1题

图17.18所示是用运算放大器构成的音频信号发生器的简化电路。

(1)R1大致调到多大才能起振?

(2)RP为双联电位器,可从0调到14.4kΩ,试求振荡频率的调节范围。

第2题

题图是用运算放大器构成的音频信号发生器的简化电路。(1) R1大致调到多大才能起振?(2) RP为双联电位器,可从0调到14.4kΩ,试求振荡频率的调节范围。

第4题

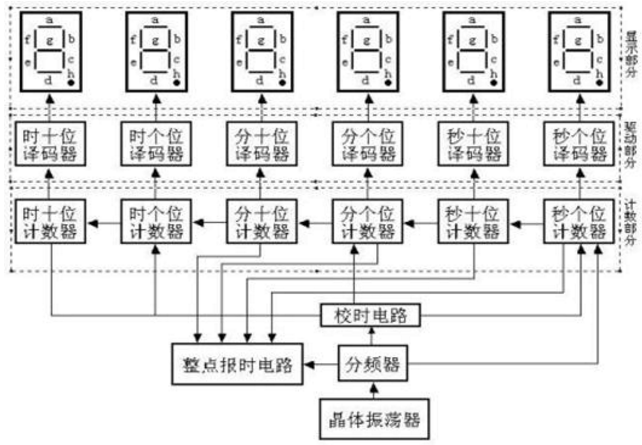

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

第6题

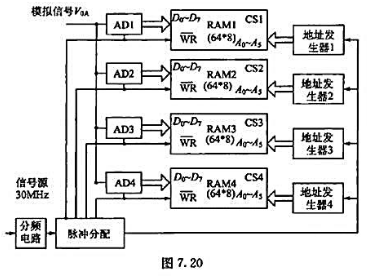

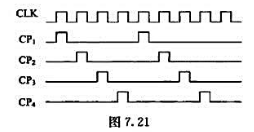

某系统为了提高采样速率,采用4片模数(全并行A/D)转换器构成并行交替式数据采集系统,原理框图如图7.20所示.系统信号源为30MHz的方波,时钟信号CLK为10MHz(要求占空比为1:1).并行交替式数据采集系统利用4片ADC轮流对同一个模拟输入信号进行采样,分别存人各路对应的64单元的存储器中,其对应各路AD所需的采样信号波形如图7.21所示,脉冲分配电路可用计数器+译码器构成.试根据系统设计参数要求,完成各部分电路的设计,器件任选.

(1)分频电路;

(2)脉冲分配电路;

(3)地址发生器电路设计;

(4)说明每个地址发生器所使用的时钟信号分别是什么?

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧