题目内容

(请给出正确答案)

[主观题]

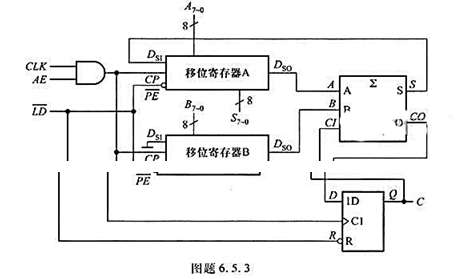

用一个全加器和一个D触发器及两个8位移位寄存器A、B构成的8位串行加法电路如下图所示。图中,CLK为时钟输入端;

为置数控制输入端,当

为置数控制输入端,当 时,8位被加数A7~0和8位加数B7~0。将分别进入移位寄存器A和B;AE为加运算控制端,当AE=1时,进行串行加法运算,输入8个时钟脉冲后恢复为0;S7~0。为8位和输出端;C为进位输出端。移位寄存器A、B的CP端为时钟输入端,

时,8位被加数A7~0和8位加数B7~0。将分别进入移位寄存器A和B;AE为加运算控制端,当AE=1时,进行串行加法运算,输入8个时钟脉冲后恢复为0;S7~0。为8位和输出端;C为进位输出端。移位寄存器A、B的CP端为时钟输入端, 端为并行置数控制端,Dst和Dso段分别为串行数据输入端、输出端。试分析电路的工作原理。

端为并行置数控制端,Dst和Dso段分别为串行数据输入端、输出端。试分析电路的工作原理。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

为置数控制输入端,当

为置数控制输入端,当 端为并行置数控制端,DS1和DS0端分别为串行数据输入端、输出端。试分析电路的工作原理。

端为并行置数控制端,DS1和DS0端分别为串行数据输入端、输出端。试分析电路的工作原理。

.jpg)

.jpg)

.jpg)

.jpg)