加法器电路

试利用二进制并行加法器74LS283和必要的门电路组成1个二-十进制加法器电路(提示:根据BCD码中8421码的加法运算规则,当两数之和小于等于9(1001)时,相加的结果与按二进制数相加所得到的结果一样。当两数之和大于9(即等于1010~1111)时,应按在二进制数相加的结果上加6(0110),这样就可以给出进行信号,同时得到一个小于9的和)。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

试利用二进制并行加法器74LS283和必要的门电路组成1个二-十进制加法器电路(提示:根据BCD码中8421码的加法运算规则,当两数之和小于等于9(1001)时,相加的结果与按二进制数相加所得到的结果一样。当两数之和大于9(即等于1010~1111)时,应按在二进制数相加的结果上加6(0110),这样就可以给出进行信号,同时得到一个小于9的和)。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“加法器电路”相关的问题

更多“加法器电路”相关的问题

第1题

试利用二进制并行加法器74LS283和必要的门电路组成1个二-十进制加法器电路(提示:根据BCD码中8421码的加法运算规则,当两数之和小于等于9(1001)时,相加的结果与按二进制数相加所得到的结果一样。当两数之和大于9(即等于1010~1111)时,应按在二进制数相加的结果上加6(0110),这样就可以给出进行信号,同时得到一个小于9的和)。

第2题

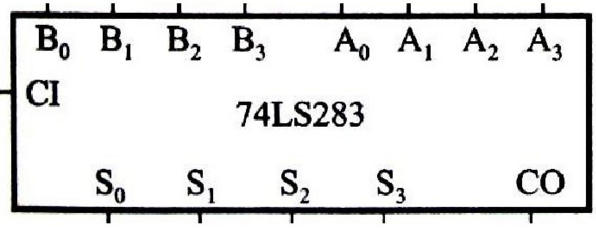

试用四位并行加法器74LS283设计一个加/减运算电路,当控制信号M=0时它将两个输入四位二进制数相加,而M=1时,它将两个四位二进制数相减。允许附加必要的门电路。74LS283的框图如图3.2.22所示。

第3题

试用4位并行加法器74LS283设计一个加/减运算电路。当控制信号K=0时将两个输入的4位二进制数相加,而K=1时它将两个输入的4位二进制数相减,允许附加必要的门电路。

第5题

试用4位并行加法器74LS283设计一个加/减运算电路。当控制信号M=0时它将两个输入的4位二进制数相加,而M=1时它将两个输入的4位二进制数相减。两数相加的绝对值不大于15。允许附加必要的门电路。

第7题

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧