题目内容

(请给出正确答案)

[主观题]

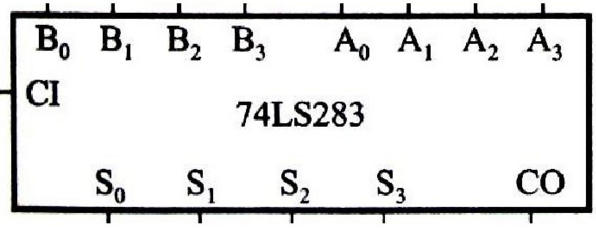

设计一个能实现两个1位二进制数的全加运算和全减运算的组合逻辑电路。加减控制信号用M表示,当M=0时为全加运算,M≈1时为全减运算。要求: (1)用最少个数的与非门实现(画出逻辑电路图): (2)用74X151实现(画出逻辑电路图); (3)用74X138加必要的门电路实现(画出逻辑电路图).

设计一个能实现两个1位二进制数的全加运算和全减运算的组合逻辑电路。加减控制信号用M表示,当M=0时为全加运算,M≈1时为全减运算。要求: (1)用最少个数的与非门实现(画出逻辑电路图): (2)用74X151实现(画出逻辑电路图); (3)用74X138加必要的门电路实现(画出逻辑电路图).

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案