题目内容

(请给出正确答案)

[主观题]

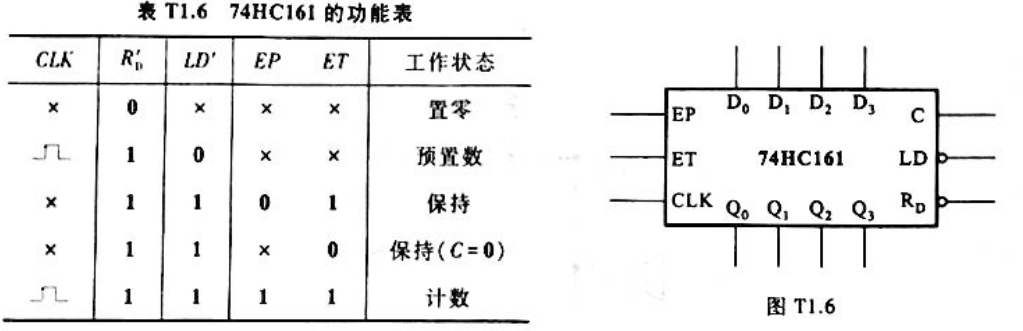

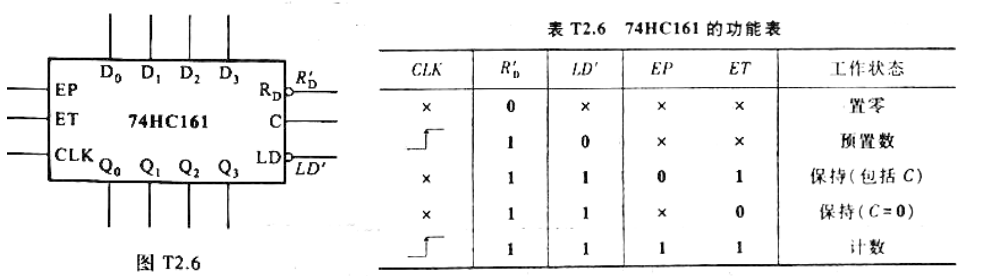

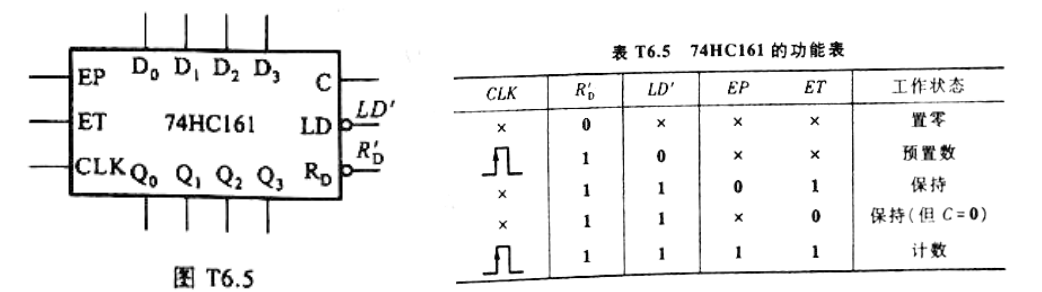

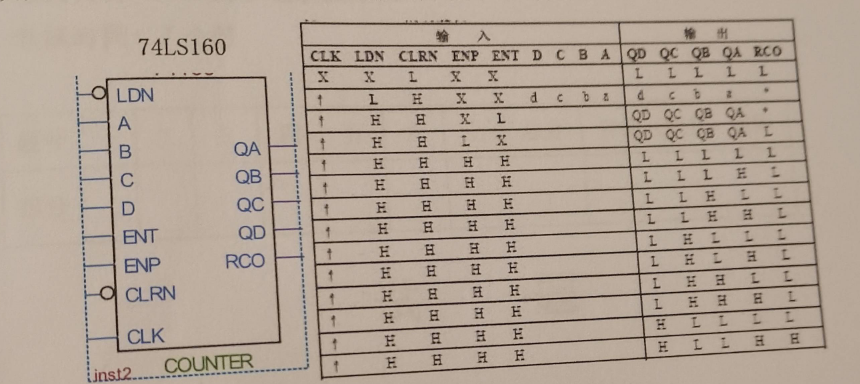

设计一个可控进制的计数器,当M=0时工作在八进制,M=1时工作在六进制。(1)只用一片同步十进制计数器74LS160及适当的门电路设计并给出设计原理及电路,74160的电路符号及功能表如图所示;(2)用JK触发器和门电路设计,要求电路最简,判断能否自启动。给出状态转换图,状态方程、驱动方程、输出方程。

设计一个可控进制的计数器,当M=0时工作在八进制,M=1时工作在六进制。(1)只用一片同步十进制计数器74LS160及适当的门电路设计并给出设计原理及电路,74160的电路符号及功能表如图所示;(2)用JK触发器和门电路设计,要求电路最简,判断能否自启动。给出状态转换图,状态方程、驱动方程、输出方程。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案