题目内容

(请给出正确答案)

[主观题]

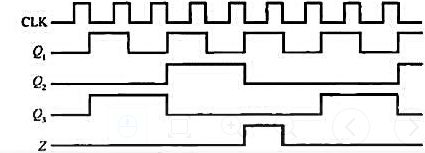

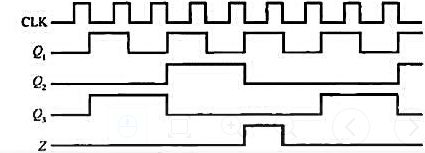

设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q3及输出Z的波形图如图3.27所示

,用JK触发器实现.Q3为高位,Q1为低位.

图3.27

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

图3.27

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q…”相关的问题

更多“设计一个计数器,在CLK脉冲作用下,三个触发器Q1、Q2、Q…”相关的问题

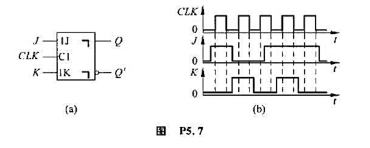

第1题

画出图P5.7(a)中脉冲触发JK触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入J、K的电压波形如图P5.7(b)所示。设触发器的初始状态为Q=0。

第2题

设计一个波形发生器,其输入为CP脉冲,输出Z的波形如图7.3.27所示。 (1)用触发器和门电路完成上述设计。 (2)试用MSI移存器74LS195和门电路完成上述设计。 (3)用VHDL语言完成上述设计。

1.jpg)

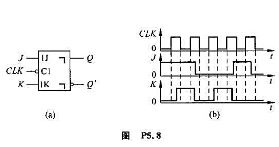

第3题

图P5.8(b)所示。设触发器的初始状态为Q=0。

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧