题目内容

(请给出正确答案)

[主观题]

如果要求用计数器CT74161和4-16译码器设计一个12路输出的脉冲分配器,即从电路的12个输出端顺序、循环地输出与时钟正脉冲等宽的负脉冲,则电路应如何连接?试设计电路,井画出电路图.

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“如果要求用计数器CT74161和4-16译码器设计一个12路…”相关的问题

更多“如果要求用计数器CT74161和4-16译码器设计一个12路…”相关的问题

第1题

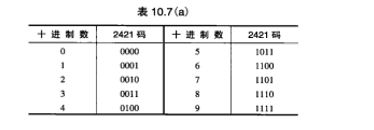

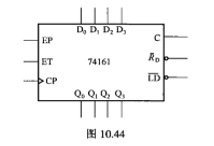

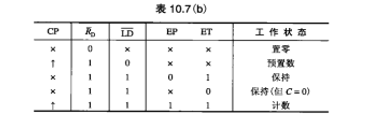

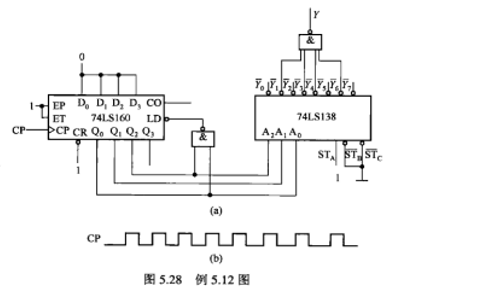

试利用同步十六进制计数器74LS161和4线-16线译码器74LS154设计节拍脉冲发生器,要求从12个输出端顺序、循环地输出等宽的负脉冲。

第2题

第3题

有效,使能端处于有效状态.

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.

第5题

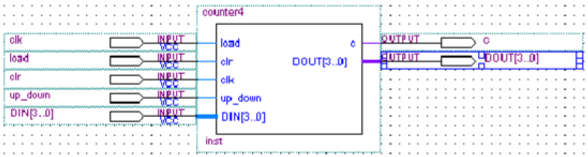

4位二进制加法计数器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计4位二进制加法计数器电路,建立4位二进制加法计数器的实验模式。通过电路仿真和硬件验证,进一步了解4位二进制加法计数器的功能和特性。

设计原理

4位二进制加法计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;CLRN是复位输入端,低电平有效;Q[3..0]是计数器的状态输出端;COUT是进位输出端。

第6题

A、译码器不一定是一个最小项发生器

B、3-8译码器是一个最小项发生器

C、译码器可以作为数据分配器使用

D、在负逻辑约定中,译码器输出端低有效表示输出0有效

第8题

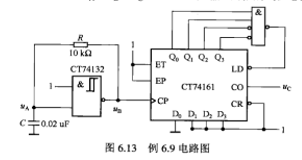

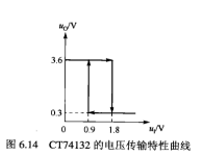

(1)分别指出图6.13中两部分电路组成什么功能的电路(名称).

(2)分析CT74161组成的电路,画出状态转换图.

(3)试画出uA、uB、uC(CO为进位输出端)的对应波形.

第11题

试用一片集成四位二进制加法计数器74LS161和一片3/8线译码器74LS138组成一个五节拍顺序脉冲发生器。

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧