设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制数序列000、 001、010、011、 100、101、110、111计数并重复。当X=1时,计数器以格雷码序列000、001、 011、 010、 110、111、101、100计数并重复,要求:(1)画出计数器的状态图和ASM图;(2)用Verilog HDL语言描述系统的工作过程。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制…”相关的问题

更多“设计一个可以控制计数功能的计数器,当X=0时,计数器以二进制…”相关的问题

第1题

用PAL16R6设计一个4位二进制计数器,要求:

(1)具有并行置数功能。并行数据输入为P0,P1,P2,P3,控制信号为。当

时并行置数;当

时计数。

(2)具有加/减计数功能。控制信号为,当

且

时为加计数;当

且

时为减计数。

(3)具有并行输出Q0,Q1,Q2,Q3。

(4)具有进位输出C和借位输出B。

第3题

设计一个可控进制计数器,当控制输入M=0时为七进制计数,当M=1时为十三进制计数。 (1)试用MSI计数器设计该可控计数器。 (2)用VHDL语言设计该可控计数器。

第4题

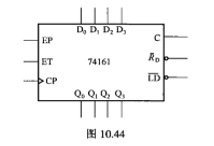

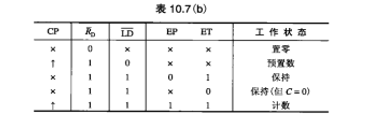

用一片如图A1-4所示的4位二进制加法计数器74161和必要的逻辑门电路设计一个可控计数器,要求当控制信号M=1时,实现七进制计数器;而当控制信号M=0时,实现十三进制计数器。画出所设计的可控计数器的逻辑电路。

第6题

试用 Verilog语言描述一个4位二进制可逆计数器的行为。要求如下:

(1)电路具有5种功能,即异步清零、同步置数、递增计数、递减计数和保持原有状态不变。且要求计数器能输出进位信号和借位信号,即当计数器递增计数到最大值时,产生一个高平有效的进位信号C0;当计数器递减计数到最小值0时,产生一个高电平有效的借位信号B0。

(2)用QuartusI软件进行逻辑功能仿真,并给出仿真波形。

第7题

第8题

第10题

A.计数器0工作在模式1

B.计数器1工作在模式5

C.计数器1按二进制计数方式工作

D.计数器2按二进制计数方式工作

E.计数器2工作在模式5

第11题

试用JK触发器设计一个变模计数器,要求: (1)控制端X=0时,计数器的模M=3,计数规律为

1.jpg) (2)控制端X=1时,计数器的模M=4,计数规律为

(2)控制端X=1时,计数器的模M=4,计数规律为

2.jpg) 试画出逻辑电路图。

试画出逻辑电路图。

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧