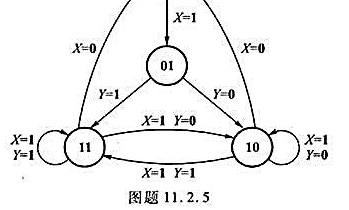

一个数字系统控制单元的状态图如图题11.2.5所示,试画出等效的ASM图(状态框是空的),并用D触发器

一个数字系统控制单元的状态图如图题11.2.5所示,试画出等效的ASM图(状态框是空的),并用D触发器和数据选择器实现控制单元电路。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

一个数字系统控制单元的状态图如图题11.2.5所示,试画出等效的ASM图(状态框是空的),并用D触发器和数据选择器实现控制单元电路。

如搜索结果不匹配,请 联系老师 获取答案

如搜索结果不匹配,请 联系老师 获取答案

更多“一个数字系统控制单元的状态图如图题11.2.5所示,试画出等…”相关的问题

更多“一个数字系统控制单元的状态图如图题11.2.5所示,试画出等…”相关的问题

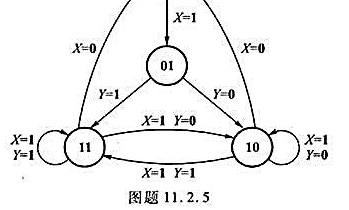

第2题

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

第5题

图10.17(a)、(b)、(c)、(d)所示各触发器中,设触发器初始状态为0,并已知时钟脉冲CP的波形如图10.17(e)所示。试画出各触发器Q1,Q2,Q3,Q4的波形。

第6题

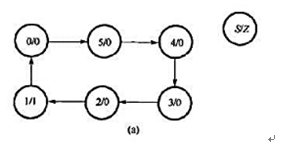

下图所示各触发器中,设触发器初始状态为0,并已知时钟脉冲CP的波形如图(b)所示。试画出各触发器输出端Q的波形。

第8题

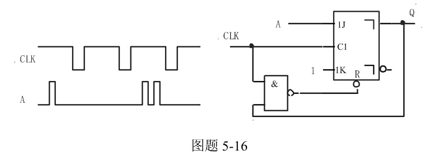

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

第9题

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

第10题

如图(a)同步RS触发器CP、R、S端的输入波形如图(b)所示,试画出Q和 的波形图。设初始状态Q=0、

的波形图。设初始状态Q=0、 =0

=0

第11题

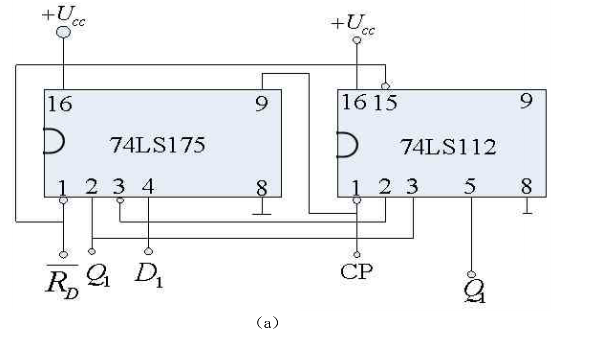

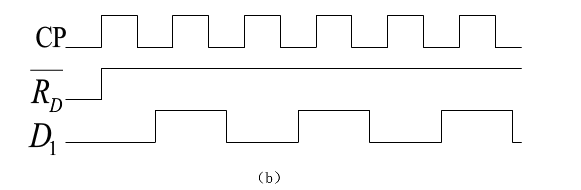

74LS175型四上升沿D触发器和74LS112型双下降沿JK触发器的接线图如图 21.40(a)所示,它们的外引线排列分别见教材图21.6.4(b)和教材图21.11(b)。(1)试按图画出逻辑电路;(2)设CP, ,D1的波形如图21.40(b)所示,试画出两触发器输出端Q的波形。两触发器的初始状态均为0。

,D1的波形如图21.40(b)所示,试画出两触发器输出端Q的波形。两触发器的初始状态均为0。

为了保护您的账号安全,请在“赏学吧”公众号进行验证,点击“官网服务”-“账号验证”后输入验证码“”完成验证,验证成功后方可继续查看答案!

微信搜一搜

微信搜一搜

赏学吧

赏学吧

微信搜一搜

微信搜一搜

赏学吧

赏学吧